1、首先在项目上右键,新建,在新建界面选择IP Core(IP核),命名并创建。

然后会自动打开New Source Wizard,展开Memories & Storage Elements, 展开RAMs & ROMs,可以找到Block Memory Generator。

2、打开这个Generator,来到如图界面,左边是当前将要创建的Memory的输入输出。稍后的设置会调整这些端口。点击Next.

3、在第二步(Page 2 of 6),选择Simple Dual Port RAM,如果两个端口时钟相同也可以勾选Common Clock简化输入输出以及内部设计。

可以看到左边的端口有了地址端口ADDRA,ADDRB,输入DINA,输出DOUTB。还有A口写使能WEA,以及两个端口的CLKA和CLKB。

4、再下一步,设置Port A Options。包括数据宽度Write Width,和存储单元个数Write Depth。如图设置64个存储单元,对应的地址线6根。

Port B只需要自动跟随A的设置即可(读端口)。

5、在第四步,下面的Memory Initialization设置存储器的初始化。勾选Load Init File以选择coe文件。

6、coe文件实质上是文本文件。我们使用记事本新建并编辑。

先写memory_initialization_radix=进制;

再写memory_initialization_vector=各单元数据逗号隔开;

编辑好后,保存并修改后缀为coe.

7、如果导入成功,则会显示COE File Contents窗口,且没有红色的错误提示。

可以上下滚动查看各个Index的初始值是否符合预期。

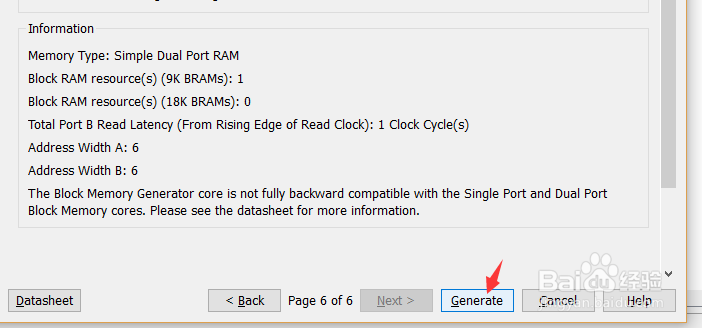

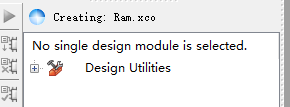

8、然后点击Generate。需要等待一段时间。完成后,我们就可以在代码中使用这个名称的模块了。

比如我新建的这个是Ram,那么我就可以 Ram myram(.CLKA(clk)...)去调用它了。